케이던스(Cadence Design Systems)가 Arm의 유니버시티 프로그램(Arm University Program, AUP)과 협력하여 Arm의 “VLSI 기초과정 – 실습 교육키트”에 케이던스의 디지털 임플리멘테이션 소프트웨어를 활용한다.

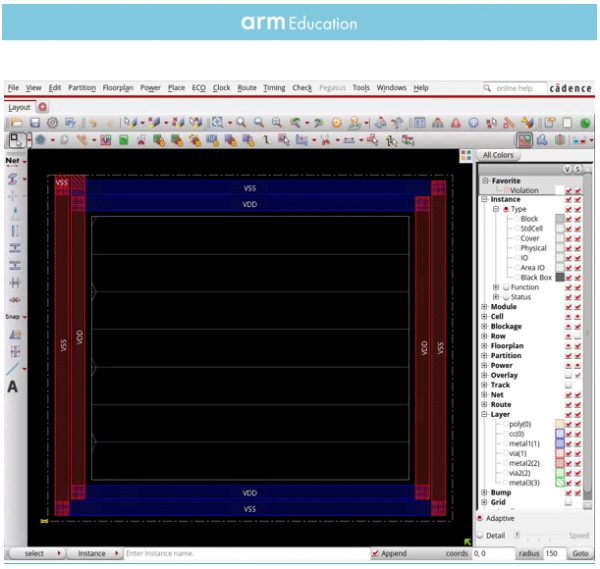

VLSI(very large scale integrated circuit) 교육키트는 Arm의 유니버시티 프로그램인 AUP에서 작년에 발표한 실습 교육키트로, 20개의 모듈이 포함되어 있다. 그리고 강의 슬라이드 및 실습으로 구성되어 10-12주짜리 일반 학부 과정에 적용할 수 있다. VLSI 교육키트는 케이던스 아카데미 키트(Cadence Academic Kits)에서 내놓은 첫 결과물이다.

에든버러 대학의 다니엘 치트니스 (Danial Chitnis) 박사는 “VLSI 기초과정은 트랜지스터 이론에서 마이크로프로세서 아키텍처에 이르기까지 다양한 주제를 다루고 있으며, 칩 설계 과정에서 간과하기 쉬운 레이아웃 설계, 제조공정(fabrication) 기술 및 테스트를 포함한 실습 주제도 다루고 있다”고 설명했다.

그는 이어 “VLSI 과정은 칩 설계의 모든 측면을 가르치고 배울 수 있는 실습방식으로, 선행 CMOS 공정의 트랜지스터 스케일링과 그것이 회로설계에 미치는 영향을 포함하여 집적회로 개발에 필요한 과제를 다룬다”고 말했다.

VLSI 교육키트로 학생들은 전기장 효과, 채널길이 변조, 문턱 전압 효과 및 누출로 인한 비이상적 트랜지스터의 특성, 잡음, 직류(DC) 응답 및 RC 지연 모델을 포함한 CMOS 회로의 특성 추정 방법을 배울 수 있다.

온칩(on-chip) 와이어의 저항, 정전 용량 추정, 온칩(on-chip) 와이어에서 와이어 지연, 전력소비 및 혼선 최적화 방법, CMOS 래치, 플립-플롭(flip-flop) 작동 및 스틱 다이어그램(stick diagram)을 이용한 플랜 셀(plan cell) 레이아웃, 설정 및 유지 시간과 같은 타이밍 제약에 의해 부과되는 한계, 순차회로의 전파 및 오염 지연 등에 대해서도 학습할 수 있다.

이외에도, 칩 설계에서 다양한 지식을 습득할 수 있어 VLSI에 대한 이해를 심화시킬 수 있는데, 예를 들면 테스트의 중요성과 고장 고착, 자동 테스트 패턴 생성(Automatic Test Pattern Generation), 내장된 자체 테스트 기능(Built in Self-Test), 다른 SRAM 아키텍처, 회로의 전원 소산원, 전력손실 제어, 클럭 분배망 스큐(skew) 및 클럭 전력소비에 미치는 영향, 온칩 변동의 원인 및 효과, DC 전송 특성, 과도 응답 및 전력 소비량 파악을 위해 SPICE(Simulation Program with Integrated Circuit Emphasis)를 이용한 회로 시뮬레이션 방법 등 심화학습이 가능하다.