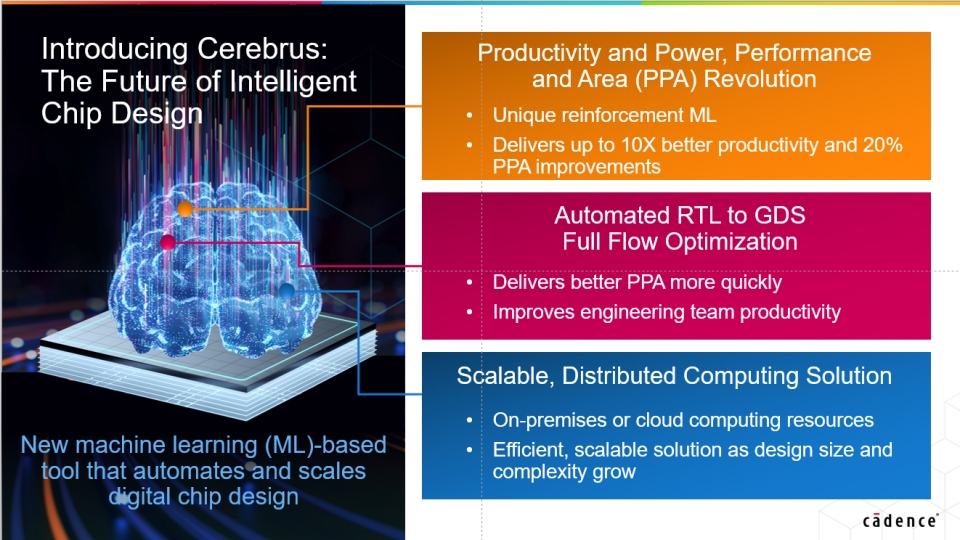

반도체설계자동화(EDA) 툴 업체인 케이던스(Cadence Design Systems)가 디지털 칩의 설계 자동화를 위해 머신러닝 기반의 ‘Cerebrus’를 출시했다.

Cerebrus는 강화된 머신러닝을 통해 디자인 설계 탐색이 어려운 플로우 솔루션을 신속하게 찾아냄으로써 생산성 향상 및 20% 소비 전력 감소로 PPA(Power Performance Area)를 개선시킨다.

설명에 따르면 신제품 ‘Cerebrus’와 케이던스 시스템 반도체 사인오프(Cadence RTL-to-signoff) 플로우의 조합은 칩 설계자, CAD 및 IP 개발자들이 기존에 수작업으로 하던 방식에 비해 생산성을 최대 10배 향상하는 동시에 전력과 PPA를 최대 20%까지 개선할 수 있다.

김상윤 삼성 파운드리 설계기술부문 상무는 “우리는 최신 반도체 공정을 계속 제공하고 있기 때문에 설계기술 협력 최적화 프로그램인 DTCO(Design Technology Co-Optimization)에서 효율성을 중요하게 생각한다”며 “삼성 파운드리는 케이던스와의 장기적인 파트너십 일환으로 Cerebrus 및 케이던스 디지털 구현 플로우를 여러 애플리케이션 제품에 사용해 왔다. 이를 통해 수개월이 걸리던 작업이 단 며칠 만에 가장 중요한 설계 블록 일부에서 8% 이상의 전력 절감 효과를 확인하게 됐다”고 말했다.

저작권자 © MSD(Motion System Design) 무단전재 및 재배포 금지